【01研究背景】

忆阻器是下一代信息存储和类脑神经形态计算的重要选择之一。其中,阻变介质层材料在忆阻器结构设计中扮演着至关重要的角色。而二维材料具有层状结构、原子级厚度和表面无悬挂键的特性,使它们能够像乐高积木一样构建各种各样的范德华异质结。二维材料忆阻器通常采用三明治式的垂直结构,这种结构易于堆叠,可以高密度集成。然而,随着二维半导体阻变层的厚度减小到纳米级,其窄带隙和残余导电细丝的存在会产生较大的关态电流,从而消耗额外的静态功耗。因此,减少二维半导体忆阻器的关态电流是一个亟待解决的问题。

目前已提出了几种降低二维半导体忆阻器关态电流的方法,包括选通器与忆阻器结合、引入表面自组装氧化层,以及原位沉积超薄的金属氧化物等。其中,原位沉积金属氧化物被认为是一种有效的方法。然而,由于维半导体表面没有悬挂键,导致原位沉积的金属氧化物与二维半导体之间的界面质量较差,进而影响器件性能。六方氮化硼(h-BN)不仅具有高禁带宽度,而且与其他二维材料堆叠时,具有原子级平整的界面,可以作为一种理想的界面绝缘层,构筑高质量界面并降低忆阻器的关态电流。

【02成果介绍】

近日,复旦大学光电研究院的褚君浩院士/李文武教授团队,从优化器件结构的角度出发,在二维In2Se3半导体和顶电极之间引入超薄的h-BN界面层,增加界面肖特基势垒,显著降低In2Se3忆阻器的关态电流。此外,h-BN界面层,在热蒸镀过程中有效避免了高能金属原子损伤二维半导体表面,在二维半导体和h-BN之间构筑了高质量的范德华界面。

研究结果表明,具有最佳h-BN界面层厚度的石墨烯/α-In2Se3/h-BN/Au范德华异质结忆阻器,表现出超低的关态电流(~pA量级)。与没有h-BN界面层的忆阻器相比,其关态电流降低了5个数量级。此外,该器件的低阻态/高阻态的电流开关比高达109, 为多电阻态调控提供更宽的电流调节范围,进而实际量测出32个非易失性的电阻态,为低功耗忆阻器的设计提供了一种新的设计思路。研究结果以“Ultralow Off-State Current and Multilevel Resistance State in Van der Waals Heterostructure Memristors”为题发表在《Advanced Functional Materials》期刊上,博士研究生刘新领为第一作者,李文武教授为通讯作者。

【03数据概览】

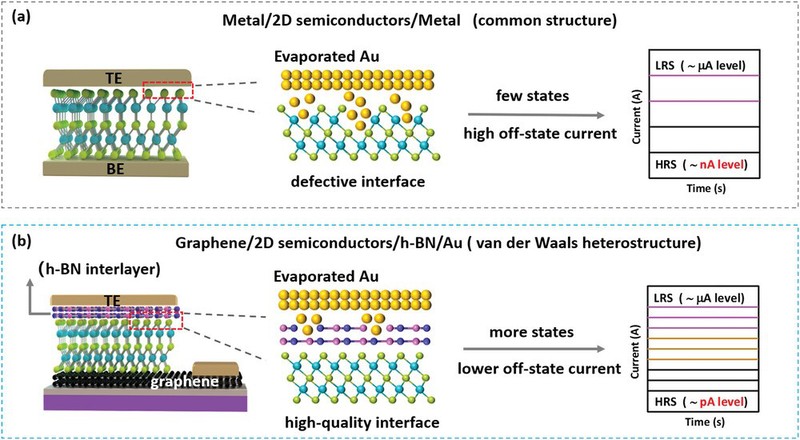

图1. 传统结构和范德华异质结构忆阻器对比:(a)传统金属/2D半导体/金属堆叠忆阻器,在二维半导体/顶电极之间存在缺陷的界面。(b)石墨烯/α-ln2Se3/h-BN/金范德华异质结构忆阻器,在二维半导体/h-BN之间存在高质量的界面。

图1a是金属/二维半导体/金属忆阻器的结构示意图,包括底部电极、二维阻变介质层和顶部电极。在热蒸发过程中,高能金属原子会扩散到阻变层中,在二维半导体表面与顶电极之间形成缺陷界面。此外,由于二维半导体较低的禁带宽度和重置后残余导电细丝的存在,忆阻器具有较大的关态电流(达到~nA量级)。图1b是石墨烯/α-In2Se3/h-BN/金属的范德华异质结忆阻器的结构示意图。在α-In2Se3和顶电极之间引入超薄的h-BN界面层,一方面h-BN界面层增加了界面的肖特基势垒高度,影响电子的传输,从而抑制关态电流,另一方面h-BN界面层,在热蒸发过程中也可以避免高能金属原子轰击二维半导体表面,在二维半导体和h-BN界面层之间形成高质量的范德华界面。此外,高的电流开关比,也为忆阻器的多阻态调控提供了更宽的电流调节范围。

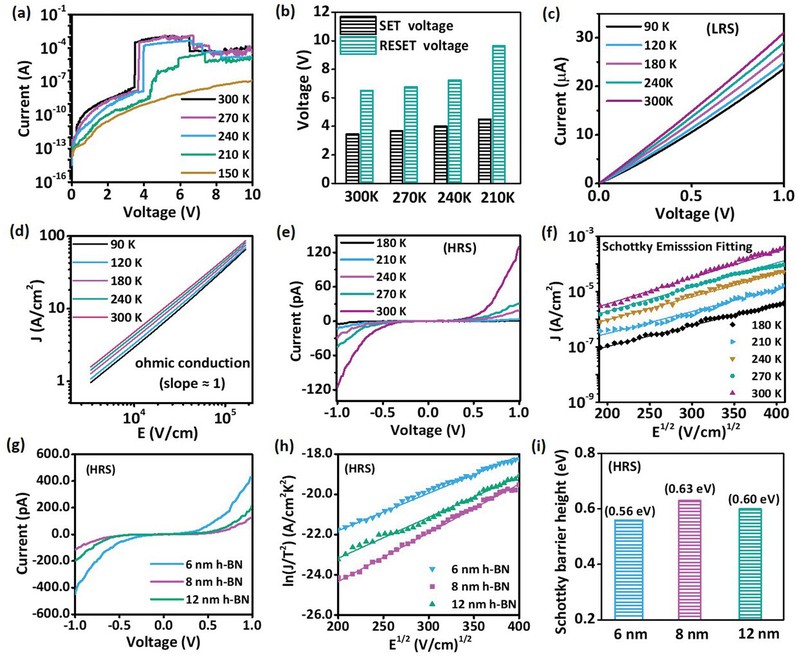

图2. 石墨烯/α-ln2Se3/h-BN/金范德华异质结忆阻器的电学性能(其中,h-BN厚度为8nm)。(a)忆阻器的I-V曲线。(b) 写入SET和重置RESET电压统计分布。(c)对数-对数坐标I-V曲线。(d)高阻态HRS和低阻态LRS的I-V曲线。(e)施加不同SET和RESET电压后电阻态的保持曲线。(f)施加不同的电压脉冲所记录的32个电阻态。(g) HRS和LRS状态下的保持稳定性。

图2展示了石墨烯/α-In2Se3/h-BN/Cr-Au范德华异质结忆阻器的电学性能,均表现为单极性的阻变翻转类型。在读取电压为0.1 V时,该器件的开态电流为1.3×10-5 A,关态电流为1.2×10-14 A,低阻态/高阻态电流开关比高达109,静态功耗低至1.2 fW。大的电流开关比使得器件具有更宽的电流调节范围,通过施加不同的电压脉冲,可量测出32个非易失性的电阻态,并且在1000秒的测量期间表现出良好的稳定性。

图3. 温度依赖的I-V曲线及导电机制分析。(a)在不同温度下测量的I-V曲线。(b)不同温度下的SET和RESET 电压(c)LRS状态温度相关的I-V曲线。(d)欧姆传导拟合曲线。(e)HRS状态温度相关的I-V曲线。(f)肖特基发射拟合曲线。(g)在相同复位电压和300 K条件下,具有不同h-BN层厚度的忆阻器的I-V曲线。(h)肖特基势垒高度拟合。(i)提取的肖特基势垒高度值。

结合变温测试,进一步分析石墨烯/α-In2Se3/h-BN/Cr-Au忆阻器的导电机制。图3a显示在300~150 K温度下的I-V曲线。随着温度降低,需要更高的写入SET/重置RESET电压来形成/破坏导电细丝。当温度低于150 K时,由于空位的激发不足而无法形成导电丝,电阻切换行为消失。在低阻态LRS时,电流密度与电场呈线性关系,符合欧姆传导拟合模型,电子遵循最近邻跳跃机制进行传导。电子从一个陷阱态跳到最近的陷阱态,然后隧穿通过h-BN界面层,完成传导过程。在高阻态HRS中,I-V曲线呈非线性关系(图3e),表明存在界面肖特基势垒,且符合肖特基发射模型(图3f)。在相同RESET电压和300 K测量温度下,进一步拟合出不同h-BN界面层厚度所对应的肖特基势垒高度(图3h)。

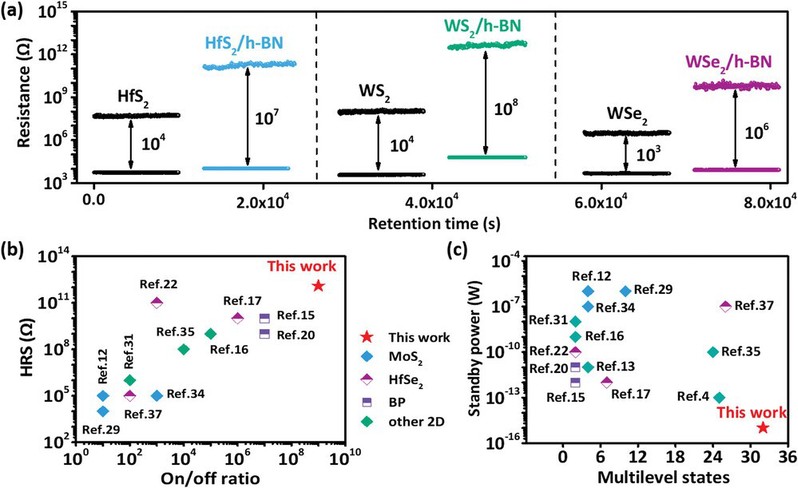

图4.(a)有无h-BN界面层的HfS2、WS2和WSe2忆阻器在HRS和LRS状态下的保持性能。(b和c)石墨烯/α-ln2Se3/h-BN/Cr-Au范德华忆阻器与最近报道的忆阻器性能参数比较。

图4展示该方法也适用于其他二维半导体忆阻器,例如HfS2、WS2和WSe2,突出其方法的适用性。图4b和c比较了石墨烯/α-In2Se3/h-BN/Cr-Au忆阻器和近五年来报道的其他二维忆阻器的性能参数,包括高阻态值,电流开/关比,静态功耗和多电阻状态。具有h-BN界面层的忆阻器的主要优点是同时实现了超低静态功耗、大电流开关比和多电阻态。

【04总结与展望】

本文通过在二维半导体和顶电极之间引入薄的h-BN界面层,显著降低了忆阻器的关态电流。其中,具有8 nm h-BN界面层的石墨烯/α-In2Se3/h-BN/Cr-Au忆阻器,与没有h-BN中间层的忆阻器相比,其关态电流降低了5个数量级,达到pA量级。另外,该忆阻器的低阻态/高阻态电流开关比达109,可实现32个电阻态,为降低忆阻器的关态电流提供了一种技术途径。

文章信息:X. L. Liu, C. Zhang, E. L. Li, C. F. Gao, R. X. Wang, Y. Liu, F. C. Liu, W. Shi, Y. H. Yuan, J. Sun. Y-F. Lin, J. H. Chu, W. W. Li. Ultralow Off-State Current and Multilevel Resistance State in Van derWaals Heterostructure Memristors. Advanced Functional Materials 23, 2309642 (2023).

文章链接:https://onlinelibrary.wiley.com/doi/full/10.1002/adfm.202309642